XMOS

Introduction

New hardware architecture that follow a diametrically opposite approach to the Amrc Cortex in the Fab inventory: Instead of creating more and more dedicated silicon to do special tasks this architecture does it all in software: Using up to 4 cores, running 8 threads each these micro processors boast up to 1600 million instructions per second as well as single cycle Port I/O at 100mhz sampling rate.

Available Software libs:

github.xcore.comProcessors:

32bit, 8 Threads 64Kbyte Ram per Core(running at 400/500Mhz)

Available Devices

| Cores | MIPS | IOPins | Pakage | Price@qty100 | fab-ability |

| 1 | 500 | 28 | 48TQFP | 6,50 | can be hand soldered |

| 1 | 500 | 36 | 64LQFP | 7,40 | '' |

| 1 | 500 | 64 | 128LQFP | 8,50 | '' |

| 2 | 1000 | 84 | 124QFN | 14,80 | needs to be reflow soldered |

| 4 | 1600 | 88 | FB144 | 17,80 | '' |

| 4 | 1600 | 256 | FB512 | 26,60 | '' , routing with eagle ?!? |

Communication

EachCore can communicate with other Cores through X-Links at 250Mbit/s bandwidth. The X-links can be brought out and used to connect cores across multiple packages.This way you can use multiple Chips and make scalable multi-processor systems. Threads on one core can have joint RAM access.

Developement

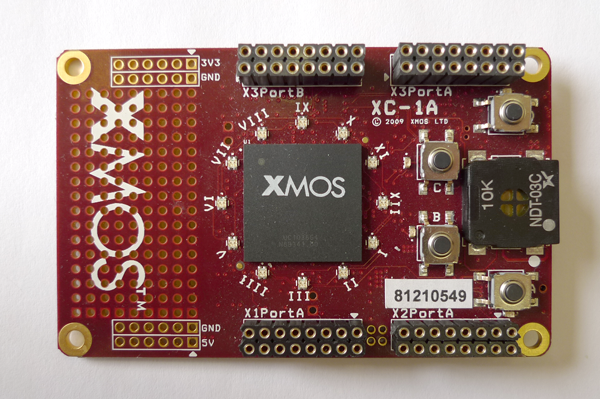

Various Dev-Boards available.

XC

In order to accommodate the congruency of tasks running on a multithreaded platform as well as low level access to ports "xc" as a language based on c was developed as the primary platform language. Development is possible using a IDE or a set of command line tools, both are available for Win/Lin/Mac.

no interrupts, instead timing sensitive operations can run concurrently.

threads have exclusive access to ports and single cycle access. -> saving a port-state to RAM can be done in two cycles.

Ports

Ports can be buffered and clocked from various sources: Serialization and Deserialization is simple and can increase the PORT IO bandwidth. e.g.:

8 bit parallel input is clocked in from an external source and saved as 32bit word. Input clock can be as high as 60 MHz. At this rate the thread has to empty the port buffer at 15 MHz.

include <xs1.h>

in buffered port:32 inP = XS1_PORT_8A;

in port inClock = XS1_PORT_1A;

clock extclk = XS1_CLKBLK_1;

int main(void)

{

configure_clock_source(extclk,inClock);

configure_in_port(inP, extclk);

start_clock(extclk);

while (1)

{

int x;

inP :> x;

f(x);

}

}

A good alternative to other 32bit uCs when it comes to bandwidth intensive applications.

Development is fun! The ARM CortexM4 is painful in comparison.